借助该芯片,研究人员在292个不同图像上,均实现了对100个量子行走的时间步骤模拟。这款新型芯片采用CMOS兼容硅光子学方式制造,具备大规模生产潜力,未来或可用于实现量子信息处理和量子模拟,为解决数据库搜索、图同构问题提供量子加速。

这项研究名称为《在硅光子量子行走处理器上实现图论问题的量子算法求解(Implementing graph-theoretic quantum algorithms on a silicon photonic quantum walk processor)》。

一、量子行走:粒子能够“既往左又往右”

要理解国防科技大学研发的“可编程硅基光量子计算芯片”是什么,首先要理解“量子行走”的含义。

简单来说,量子行走(Quantum Walk)是经典随机行走在量子世界中的一种对应,能够形成比经典随机行走(Random Walk)更丰富和复杂的可能性。

在经典的随机行走中,一个粒子随机地绕着一个离散空间行走。单位时间内,粒子每“行走一步”的方向和位移由一个随机变量来刻画,有一半概率向左、一半概率向右。

而在量子世界中,由于受到叠加(superposition)、量子干涉(quantum interference)、纠缠(entanglement)等量子状态的干涉,粒子每“行走一次”的位移,具备着更多的可能性。

也就是说,单位时间内,粒子有可能既往左又往右。在一维链状量子比特间,粒子激发以叠加态类似于波的形式传播。

▲量子行走动态示意图(图源:松山湖材实验室)

得益于丰富的可能性,量子行走的速度远远快于经典随机行走,能够加速模式识别、计算机视觉、网络分析和导航、网站流量优化等方面应用。在基于测量的量子计算中,量子行走可以用于使用和分析大而不完美的图形状态(large but imperfect graph states)。

此前,曾有研究人员利用渐逝耦合集成波导阵列(arrays of evanescently coupled integrated waveguides),实现了5个光子的量子行走;并利用积体光学的固有稳定性,实现了数百个顶点的线性图。还有大量研究致力于利用包括光子学在内的一系列物理系统,实现量子行走的仿真模拟,或利用量子逻辑实现数字仿真。

但是,多数研究中的平面器件(planar device)受到无源底层光子电路布局(the layout of the passive underlying photonic circuit)的限制,需要额外地修改电路,以观测量子行走参数的不同变化。

二、完全可编程的硅光子器件:可实现多达100个量子行走步骤

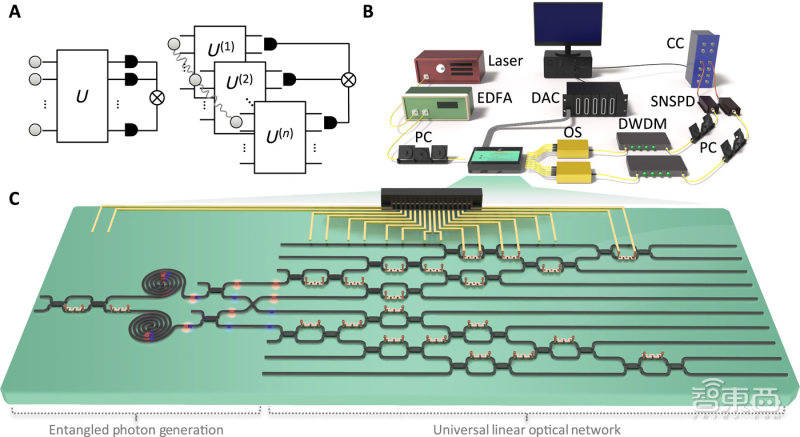

本项研究中,研究人员研发的可编程硅基光量子计算芯片尺寸为11×3平方毫米,主要由两个部分组成:纠缠光子对产生(entangled photon-pair generation)和通用线性光学变换(universal linear optical transformation)。

根据论文,这款新型芯片不仅能够模拟关联粒子的量子行走动力学,还能实现对所有重要参数的全面控制,以及具备大规模应用的前景。

论文写道:“这种方式提供了完全的可编程性和对量子行走特性的控制,因此,其相比模拟系统具备更大的灵活性和性能。相比数字量子计算机,(基于可编程硅基光量子计算芯片的)量子计算机更可能在短期内实现。”

▲可编程硅基光量子计算芯片示意图

具体来说,该可编程硅基光量子计算芯片能够控制哈密顿结构(Hamiltonian structure)、进化时间(evolution time)、粒子识别能力(particle distinguishability)、交换对称性(exchange symmetry)等重要参数。

研究人员通过对所研制光量子计算芯片的编程运行,演示了顶点搜索、图同构等图论问题量子算法的求解。结果显示,研究人员借助该芯片,在292个不同图像上均实现了100个量子行走的时间步骤模拟。

在实现较大规模应用方面,基于可编程硅基光量子计算芯片量子计算机的纠缠结构可以通过两种方式扩大,

首先,研究人员可通过增加光学网络的大小,来扩大纠缠结构。在光学网络中,研究人员可使用具有更短光学深度、更强鲁棒性的替代设计。

其次,研究人员可通过使一个广义P-partite纠缠光子态服从于广网络的P副本,来模拟具有可调粒子相关性的P-particle的量子行走。

三、用CMOS兼容硅光子学方法制造

在制造工艺方面,这款新型量子计算芯片采用CMOS兼容硅光子学方式制造,在实现大规模光网络和多光子源方面具备潜力。

根据论文,这款新型量子计算芯片利用SOI(绝缘体上硅)材料设计和制造,其表面硅层厚度为22nm 、掩埋氧化层厚度为2μm,制造过程中大致分为6步。

1、研究人员首先利用电子束刻蚀(EBL)和电感耦合等离子体(ICP)刻蚀技术,制造出一个70nm的光栅耦合器(grating couple)。

2、在此基础上,研究人员在SOI晶片上进行二次电子束刻蚀和电感耦合等离子体刻蚀,以制备波导图案。

3、然后,研究人员通过等离子体增强化学气相沉积,在芯片表面沉积一层1.5μm厚的二氧化硅层。

4、接下来,研究人员将二氧化硅层抛光为0.9μm。0.9μm的二氧化硅层将被作为硅波导和微加热器之间的隔离层,以避免潜在的光损耗。

5、之后,借助标准紫外光刻、金属沉积、剥离工艺(liftoff process),研究人员制备出150nm厚的NiCr加热器和250nm厚的Au衬底。

6、最后,芯片被分开,用线连接到印刷电路板上。

根据论文,未来,研究人员或将通过引入干涉仪的优化块设计(optimized block design)等,来进一步解决可编程硅基光量子计算芯片在量子行走模拟中的误差问题。

结语:量子计算技术有望在特定应用领域抢先落地

经典计算发展路径之下,最为重要的硬件产品――传统硅基芯片,日益面临着晶体管直径逼近物理极限的问题。基于此,量子计算、革新芯片材料等研究方向成为一大热门。

其中,量子计算应用研究尚属于初级阶段,且需要极低温的运行环境,短期内难以实现大规模落地部署。

但是,以国防科技大学的对硅基光量子计算芯片的研究为代表,量子计算技术或有望在数据库搜索、图同构问题等特定应用场景中实现抢先落地。